**DISCIPLINA:** EMC0122 - Lab. de Circuitos Lógicos

UNIDADE ACADÊMICA: Escola de Engenharia Elétrica Mecânica e Computação

CURSO: Engenharia de Computação

# EXPERIÊNCIA 1 - PORTAS LÓGICAS

#### 1. OBJETIVO

- Verificar experimentalmente o funcionamento das portas: NOT (INVERSOR), OR, AND e NAND.

- Verificar experimentalmente a universalidade da porta NAND.

- Verificar experimentalmente alguns teoremas de álgebra booleana.

## 2. MATERIAL

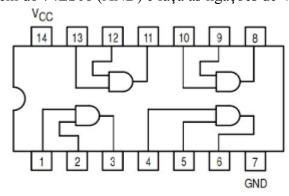

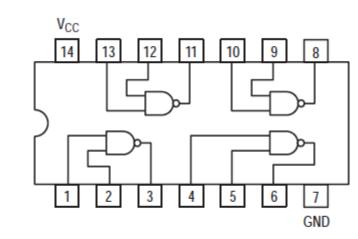

CIs: 74LS04; 74LS32; 74LS08; 74LS00 **EQUIPAMENTO -** kit – Eletrônica Digital

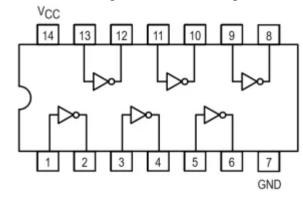

### 3. PORTA NOT ou INVERSORA - 74LS04

## Passo 1

Verifique a pinagem do 74LS04 e faça as seguintes ligações:

- o pino  $V_{CC}$  do CI ligue no terminal + 5V do kit.

- o pino **GND** do CI ligue no terminal GND do kit.

### Passo 2

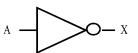

Para uma das portas lógicas do 74LS04, conecte:

A em uma das entradas das chaves geradoras de níveis lógicos.

X em uma das entradas do Leds indicadores de estado lógico.

Para os valores de A, anote na tabela o valor lido de X, onde:

- Led apagado equivale nível lógico BAIXO ou 0;

- Led aceso equivale nível lógico ALTO ou 1.

| Tab.         | 1 |   |

|--------------|---|---|

| A            | 0 | 1 |

| $\mathbf{X}$ |   |   |

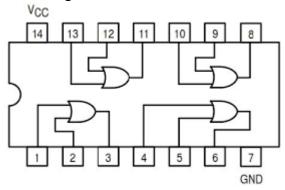

# 4. **PORTA OR - 74LS32**

## Passo 1

Verifique a pinagem do 74LS32 (OR) e faça as ligações:

- o pino  $V_{CC}$  do CI ligue no terminal + 5V do kit.

- o pino **GND** do CI ligue no terminal GND do kit.

## Passo 2

Para uma das portas lógicas, conecte:

- suas entradas em duas chaves geradoras de níveis A lógico;

B -

- sua sua saída em um dos Leds indicadores de estado lógico.

## Passo 3

Para os valores de A e B, anote na tabela o valor lido de X.

Tab. 2

| Iuc. |   |   |   |   |

|------|---|---|---|---|

| A    | 0 | 0 | 1 | 1 |

| В    | 0 | 1 | 0 | 1 |

| X    |   |   |   |   |

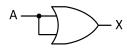

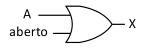

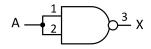

Faça as ligações de uma porta OR de duas entradas conforme mostra a figura ao lado. Determine as saídas para cada entrada indicada na tabela.

| , | Tab. | 3 |  |

|---|------|---|--|

|   | A    | 0 |  |

|   | X    |   |  |

### Passo 5

Use um porta OR de duas entradas conforme mostra a figura ao lado. Determine as saídas para cada entrada indicada na tabela.

| Tab. 4 |   |   |  |  |

|--------|---|---|--|--|

| A      | 0 | 1 |  |  |

| X      |   |   |  |  |

**OBS**: Uma entrada em aberto (flutuante) significa que não está ligada em lugar algum. No documento *Características Básicas dos CIs Digitais* você encontra as informações sobre o comportamento de entradas abertas nos dispositivos que estamos usando.

## 5. **PORTA AND - 74LS08**

#### Passo 1

Verifique a pinagem do 74LS08 (AND) e faça as ligações de Vcc e GND.

## Passo 2

Para uma das portas lógicas, conecte:

- suas entradas em duas chaves geradoras de níveis lógico;

- sua sua saída em um dos Leds indicadores de estado lógico.

Para os valores de A e B, anote na tabela o valor lido de X.

Tab. 5

| 140.5 |   |   |   |   |  |

|-------|---|---|---|---|--|

| A     | 0 | 0 | 1 | 1 |  |

| В     | 0 | 1 | 0 | 1 |  |

| X     |   |   |   |   |  |

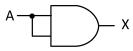

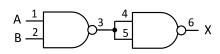

## Passo 4

Faça as ligações de uma porta AND de duas entradas conforme mostra a figura ao lado. Determine as saídas para cada entrada indicada na tabela.

| Tab. | 6 |

|------|---|

|      |   |

| A | 0 | 1 |

|---|---|---|

| X |   |   |

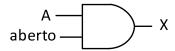

## Passo 5

Use um porta AND de duas entradas conforme mostra a figura ao lado. Determine as saídas para cada entrada indicada na tabela.

| _   | -  | _   |

|-----|----|-----|

| l'~ | I_ |     |

| 13  | n  | - 1 |

| ıч  | υ. | •   |

| A | 0 | 1 |

|---|---|---|

| X |   |   |

## 6. UNIVERSALIDADE DA PORTA NAND – 74LS00

### Passo 1

Verifique a pinagem do 74LS00 (NAND) e faça as ligações de Vcc e GND.

Para uma das portas lógicas, conecte:

suas entradas em duas chaves geradoras de níveis A lógico;

• sua sua saída em um dos Leds indicadores de estado lógico.

# Passo 3

Para os valores de A e B, anote na tabela o valor lido de X.

Tab. 8

| A | 0 | 0 | 1 | 1 |

|---|---|---|---|---|

| В | 0 | 1 | 0 | 1 |

| X |   |   |   |   |

### Passo 4

Conecte as duas entradas em um ponto comum da porta NAND. Verifique seu funcionamento. Qual operação lógica A está sendo realizada?

Tab. 9

| 140. ) |   |   |  |  |

|--------|---|---|--|--|

| A      | 0 | 1 |  |  |

| X      |   |   |  |  |

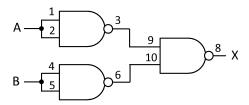

## Passo 5

Faça as conexões de duas portas NAND, como a figura ao lado. Verifique seu funcionamento. Qual operação lógica está sendo realizada?

Tab. 10

| A | 0 | 0 | 1 | 1 |

|---|---|---|---|---|

| В | 0 | 1 | 0 | 1 |

| X |   |   |   |   |

# Passo 6

Faça as conexões de três portas NAND, como a figura ao lado. Verifique seu funcionamento. Qual operação lógica está sendo realizada?

Tab. 11

| 100.11 |   |   |   |   |

|--------|---|---|---|---|

| A      | 0 | 0 | 1 | 1 |

| В      | 0 | 1 | 0 | 1 |

| X      |   |   |   |   |

| 7.         | OUESTÕES (  | Considere dis  | spositivos da | família 74.    | nas suas respo | stas) |

|------------|-------------|----------------|---------------|----------------|----------------|-------|

| <i>,</i> • | QUEST OLS ( | Constact c and | positivos aa  | 141111114 / 19 | mas suus respo | siusj |

| 7.1. | Mostre como conectar duas portas OR de duas entradas para obter o equivalente de uma porta OR de três entradas.                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.2. | Faça a tabela verdade de uma porta OR de três entradas, se uma das entradas estiver aberta.                                                                                    |

| 7.3. | Mostre como conectar duas portas AND de duas entradas para obter o equivalente de uma porta AND de três entradas.                                                              |

| 7.4. | Faça a tabela verdade de uma porta AND de três entradas, se uma das entradas estiver aberta.                                                                                   |

| 7.5. | Desenhe o circuito lógico da expressão $X = AC + BD$ usando portas AND (de duas entradas), OR (de duas entradas). Informe quantos CIs seriam necessários para a implementação. |

| 7 <b>.6.</b> | Desenhe o circuito lógico da expressão $X = AC + BD$ usando apenas portas NAND de duas entradas. Simplifique ao ao máximo a solução e informe quantos CIs seriam necessários para a implementação. |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.7.         | Nas seções 4 (portas OR) e 5 (portas AND) deste experimento, foram usados arranjos diferentes das portas. Consulte o livro texto e indique quais os teoremas (axiomas) são representados na        |

|              | (a) Seção 4, passo 4:                                                                                                                                                                              |

|              | (b) Seção 4, passo 5:                                                                                                                                                                              |

|              | (c) Seção 5, passo 4:                                                                                                                                                                              |

|              | (d) Seção 5, passo 5:                                                                                                                                                                              |

|              |                                                                                                                                                                                                    |

|              |                                                                                                                                                                                                    |